## EE 551 Linear Integrated Circuits Homework 6

Unless otherwise specified, use the following transistor parameters.

$$\begin{split} V_{T0} &= 0.7 V, \ \gamma = 0.4 V^{1/2}, \ \phi_F = 0.35 V, \ \kappa_n = \kappa_p = 0.65 \ (subthreshold), \ \mu_n = 1360 cm^2/Vs, \ \mu_p = 460 cm^2/Vs, \ K' = 100 \mu A/V^2, \ I_0 = 1 p A, \ I_0' = 0.1 p A, \ I_{th} = 1 \mu A, \ V_A = 50 V, \ K_s = 11.8, \ \epsilon_0 = 8.854 x 10^{-12} F/m, \ T = 300 K, \ V_{dd} = 5 V, \ V_{bi} = 0.7 V, \end{split}$$

- 1. For an nFET-based differential paire, answer the following questions. Assume that the input pair have W/L =  $50\mu m/0.5\mu m$ , I<sub>b</sub> = 1mA, and that  $\lambda = 0$ .

- a. What is the overdrive voltage of each transistor if V<sub>in</sub> = 0?

- b. How is the bias current shared between the two input transistors if V<sub>in</sub> = 50mV?

- c. For  $I_{out} = I_1 I_2$  and  $V_{in} = 50$ mV, what is the effective transconductance of the differential pair? Assume that this input voltage is within the linear range of the circuit.

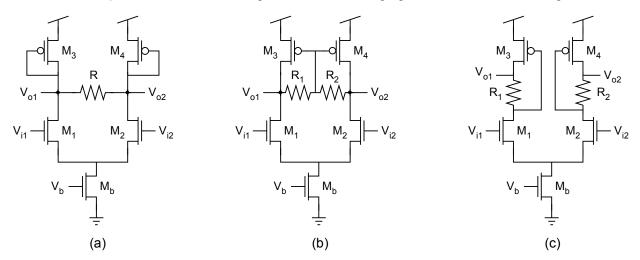

- 2. Calculate expressions for the small-signal differential voltage gain of each of the following circuits.

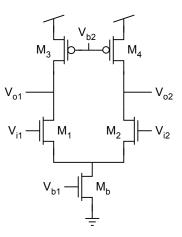

3. For the following circuit, determine the following. Assume that M1-4 have W/L ratios of  $50\mu$ m/0.5 $\mu$ m, lb = 1mA, and  $\gamma$  = 0.

- a. Determine the small-signal differential voltage gain.

- b. Determine the maximum allowable output voltage swing of  $V_{in,cm} = 1.5V$ .

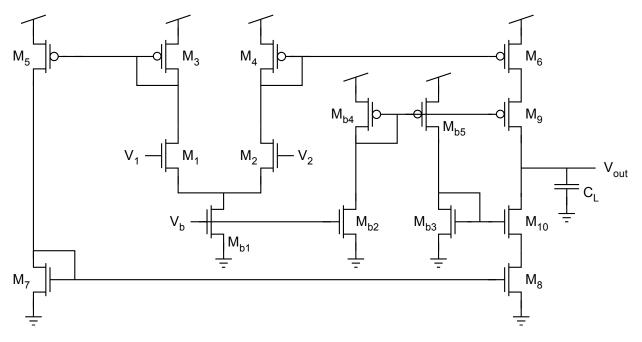

- 4. Calculate the following parameters given that  $I_{b1}$  = 100nA,  $C_L$  = 1pF,  $M_{1-10}$  and  $M_{b1}$  have W/L ratios of 10µm/1µm, and  $M_{b2-5}$  are appropriately sized to set the bias voltages for  $M_9$  and  $M_{10}$  and have 50nA flowing through them.

- a. Calculate the output resistance.

- b. Calculate the small-signal differential voltage gain.

- c. Calculate the slew rate.

- d. Calculate the power dissipation.

- e. Calculate the gain-bandwidth product, assuming that the output pole is the dominant pole.

- f. Design the sizes of  $M_{b2-5}$  to appropriately bias transistors  $M_9$  and  $M_{10}$ .